Hello I have two questions about timing diagram but I have no idea how to do them, and the due date is like 2 days away. Please help me. Thank you.

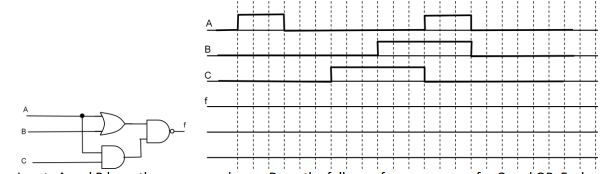

1) The circuit shown here needs to have its timing checked for specific input sequences on A, B and C.

Complete the timing diagram shown for this circuit. All gates have 1 unit delay.

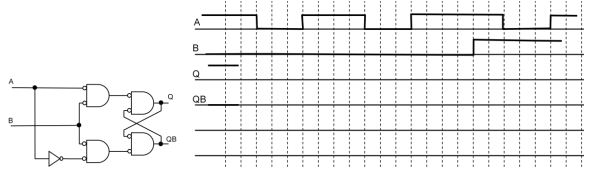

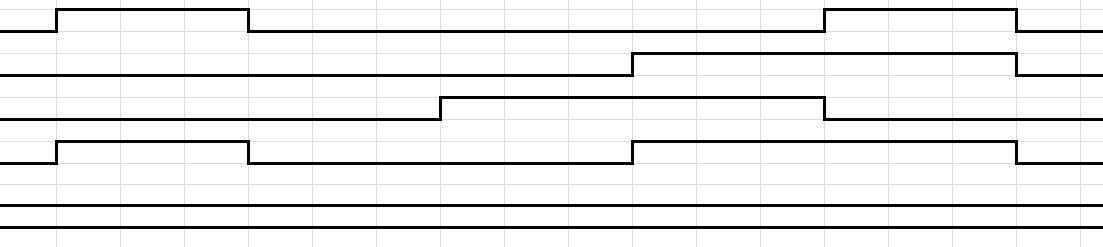

2)Inputs A and B have the sequence shown. Draw the full waveform responses for Q and QB. Each

gate has a 1 unit delay. In the sample timing chart shown the vertical lines represent that one time

unit.