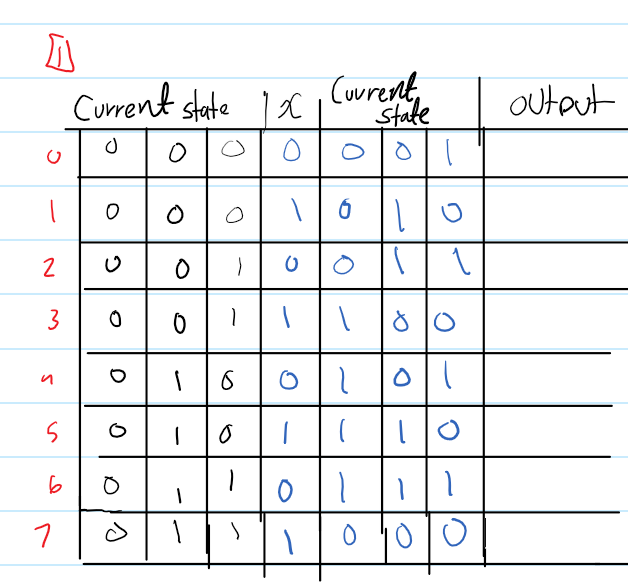

Design a three-bit counter using T-FFs. The counter has one input X. The counter counts odd numbers (1, 3, 5, 7) if X = 0 and counts even numbers (0, 2, 4, 6) if X = 1. If X = 1 and the current number is odd, the counter will go to the next even number. likewise, if X = 0 and the current number is even, the counter will go to the next odd.

**wanting to make have I did good so far ;-; been struggling a lot, next step is just drawing if I wasn't mistaken""